Mempelajari,

memahami cara kerja, dan melakukan simulasi dari rangkaian Universal JFET Bias

Curve.

a. FET

2N3819

Field

Effect Transistor atau disingkat dengan FET adalah komponen Elektronika aktif

yang menggunakan Medan Listrik untuk mengendalikan Konduktifitasnya. Field

Effect Transistor (FET) dalam bahasa Indonesia disebut dengan Transistor Efek

Medan.

b. Resistor

Resistor

adalah komponen Elektronika Pasif yang memiliki nilai resistansi atau hambatan

tertentu yang berfungsi untuk membatasi dan mengatur arus listrik dalam suatu

rangkaian Elektronika.

Cara menghitung nilai

resistansi resistor dengan gelang warna :

1. Masukan angka langsung dari kode warna gelang pertama.

2. Masukan angka langsung dari kode warna gelang kedua.

3. Masukan angka langsung dari kode warna gelang ketiga.

4. Masukkan jumlah nol dari kode warna gelang ke-4 atau pangkatkan angka tersebut dengan 10 (10^n), ini merupakan nilai toleransi dari resistor.

1. Masukan angka langsung dari kode warna gelang pertama.

2. Masukan angka langsung dari kode warna gelang kedua.

3. Masukan angka langsung dari kode warna gelang ketiga.

4. Masukkan jumlah nol dari kode warna gelang ke-4 atau pangkatkan angka tersebut dengan 10 (10^n), ini merupakan nilai toleransi dari resistor.

c. Capasitor

Polar

Kapasitor

polar adalah kelompok electrolytic terdiri dari kapasitor-kapasitor yang bahan

dielektriknya adalah lapisan metal-oksida.

Cara menghitung nilai kapasitor :

1. Masukan 2 angka pertama langsung untuk nilai kapasitor.

2. Angka ke-3 berfungsi sebagai perpangkatan (10^n) nilai kapasitor.

3. Satuan kapasitor dalam piko farad.

4. Huruf terakhir menyatakan nilai toleransi dari kapasitor.

Daftar nilai toleransi kapasitor :

B = 0.10pF

C = 0.25pF

D = 0.5pF

E = 0.5%

F = 1%

G = 2%

H = 3%

J = 5%

K = 10%

M = 20%

Z = + 80% dan -20%

1. Masukan 2 angka pertama langsung untuk nilai kapasitor.

2. Angka ke-3 berfungsi sebagai perpangkatan (10^n) nilai kapasitor.

3. Satuan kapasitor dalam piko farad.

4. Huruf terakhir menyatakan nilai toleransi dari kapasitor.

Daftar nilai toleransi kapasitor :

B = 0.10pF

C = 0.25pF

D = 0.5pF

E = 0.5%

F = 1%

G = 2%

H = 3%

J = 5%

K = 10%

M = 20%

Z = + 80% dan -20%

d. DC Generators

DC Generator berfungsi sebagai sumber tegangan DC pada

rangkaian.

e. Ground

Ground

adalah titik kembalinya arus searah atau titik kembalinya sinyal bolak

balik atau titik patokan dari berbagai titik tegangan dan sinyal listrik dalam

rangkaian elektronika.

Skala

lainnya, berlabel M, digunakan bersama dengan skala m untuk menemukan solusi

untuk konfigurasi pembagi tegangan. Penskalaan untuk m dan M berasal dari

pengembangan matematis yang melibatkan persamaan jaringan dan penskalaan

dinormalisasi yang baru saja diperkenalkan dengan persamaan:

Dengan

gambar grafik seperti dibawah ini.

Gambar. 6.58

Contoh Soal

1.

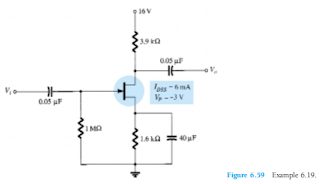

Tentukan

nilai diam ID dan VGS untuk jaringan Gambar 6.59

Solusi

Menghitung nilai m, kita dapatkan

Garis

bias diri yang didefinisikan oleh RS diplot dengan menggambar garis lurus dari

titik asal melalui titik yang ditentukan oleh m 0,31, seperti yang ditunjukkan

pada Gambar. 6.60. Q-point yang dihasilkan:

Nilai diam ID dan VGS kemudian dapat ditentukan sebagai berikut:

2.

Tentukan

nilai diam ID dan VGS untuk jaringan Gambar 6.61.

Solusi

Menghitung nilai m, kita dapatkan

Menentukan hasil VG

Untuk mencari M, kita sudah mempunyai

Sekarang

setelah m dan M diketahui, garis bias dapat digambarkan pada Gambar 6.60.

Khususnya, Perhatikan bahwa meskipun level IDSS dan VP berbeda untuk kedua

jaringan, namun kurva universal yang sama dapat digunakan. Pertama temukan M

pada sumbu M seperti yang ditunjukkan pada Gambar 6,60. Kemudian gambar garis

horizontal ke sumbu m dan, pada titik persimpangan, tambahkan besarnya m

seperti yang ditunjukkan pada gambar. Menggunakan titik yang dihasilkan pada m

sumbu dan persimpangan M, gambar garis lurus untuk memotong dengan kurva

transfer dan tentukan titik-Q:

Karena

solusi DC dari konfigurasi FET memerlukan menggambar kurva transfer setiap

analisis, kurva universal dikembangkan yang dapat digunakan untuk semua level

IDSS dan VP. Kurva universal untuk JFET n-channel atau MOSFET tipe deplesi

(untuk nilai negatif VGSQ) disediakan pada Gambar. 6.58. Perhatikan bahwa sumbu

horizontal tidak bahwa VGS tetapi dari tingkat dinormalisasi yang didefinisikan

oleh VGS / [VP], [VP] menunjukkan bahwa hanya besarnya VP yang harus digunakan,

bukan tandanya. Untuk sumbu vertikal, skala juga merupakan level ID / IDSS yang

dinormalisasi.

Hasilnya

adalah ketika ID IDSS, rasio adalah 1, dan ketika VGS VP, rasio VGS / [VP]

adalah 1. Perhatikan juga bahwa skalanya untuk ID / IDSS ada di sebelah kiri

dan bukan di kanan seperti yang ditemui untuk ID di sesi latihan sebelumnya.

Dua skala tambahan di sebelah kanan perlu dikenalkan. Skala vertikal label m

sendiri dapat digunakan untuk menemukan solusi untuk konfigurasi bias-tetap.

Tidak ada komentar:

Posting Komentar