1. Gerbang

logika XOR 2 input

2. Gerbang

logika AND 3 input

3. Gerbang

logika OR 2 input

4.

5. Resistor

6. LED

7. VCC

8. Ground

Pada percobaan 2 terdiri

atas 2 buah rangkaian yang masing-masing rangkaiannya menggunakan 1 buah

gerbang logika XOR, 1 buah gerbang logika

AND 3 input, 1 buah gerbang logika OR 2 input, 5 buah saklar, VCC,

resistor, LED, dan ground.

Rangkaian ini menggunakan 5 buah saklar SPDT untuk mengatur input awal. Ketika saklar dihubungkan ke VCC, maka input awal akan berlogika ‘1’. Dan ketika saklar dihubungkan ke ground, maka input awal akan berlogika ‘0’. Semua input dari gerbang logika XOR U1 dan gerbang logika AND U2 dihubungkan ke masing-masing saklar SPDT. Kemudian input dari gerbang logika OR U3 dihubungkan ke output gerbang logika XOR U1 dan gerbang logika AND U2. Output gerbang logika OR U3 dihubungkan dengan LED yang diserikan dengan resistor.

Prinsip kerja dari rangkaian percobaan 2 yaitu berdasarkan prinsip kerja dari gerbang logika. Pada gerbang logika XOR, outputnya akan berlogika ‘1’ ketika salah satu nilai inputnya ada yang berlogika ‘1’ atau ketika nilai dari kedua input berlainan dan akan berlogika ‘0’ ketika nilai dari kedua input sama. Untuk gerbang logika XOR yang memiliki 3 input atau lebih, cara menentukan logika dari outputnya yaitu dengan menjumlahkan semua input (logika ‘1’), jika jumlahnya bernilai ganjil, maka outputnya akan berlogika ‘1’, namun jika jumlahnya bernilai genap, maka outputnya akan berlogika ‘0’. Pada gerbang logika AND, outputnya akan berlogika ‘1’ ketika semua inputnya berlogika ‘1’. Untuk gerbang logika OR, outputnya akan berlogika ‘1’ ketika nilai inputnya ada yang berlogika ‘1’.

Pada saat kondisi inputan

awal A, B, C, dan D secara berturut-turut

adalah semuanya ‘0’, maka output yang

dihasilkan adalah ‘0’, karena output yang dihasilkan 0, maka

menyebabkan output LED mati. Ini terjadi

karena ketika kedua input pada gerbang XOR (input B dan D) berlogika 0, maka

output pada gerbang XOR adalah 0. Kemudian input gerbang AND (input A, C, dan

D) semuanya ‘0’, maka outputnya juga ‘0’.

Sehingga input gerbang OR keduanya adalah ‘0’, maka

output akhirnya juga adalah ‘0’,

kondisi LED mati. Untuk rangkaian kedua, ketika kondisi inputan awal A, B, C,

D, secara berturut-turut adalah semuanya ‘0’, maka

output yang dihasilkan adalah ‘0’, yaitu

kondisi LED mati. Ini terjadi karena ketika kedua input pada gerbang XOR (input

B dan D) berlogika ‘0’, maka output pada

gerbang XOR adalah ‘0’. Kemudian input gerbang

AND (input A, B, C) semuanya ‘0’, maka

outputnya juga ‘0’. Sehingga input gerbang

OR keduanya adalah ‘0’, maka output akhirnya

juga adalah ‘0’, kondisi LED mati.

Pada saat kondisi inputan awal A,

B, C, dan D secara berturut-turut berlogika ‘0’, ‘1’, ‘1’ ‘0’, maka input gerbang AND (input B dan D) berlogika ‘1’ dan ‘0’ sehingga gerbang logika AND akan memiliki output

berlogika ‘1’ (hasil penjumlahan input gerbang XOR

yang berlogika ‘1’ nya berjumlah ganjil) dan input

gerbang AND berlogika

‘0’, ‘0’, ‘0’ (Input A, C', dan D) sehingga gerbang logika AND akan memiliki input ‘0’ (gerbang AND akan memiliki output

berlogika 0 jika semua atau salah satu inputnya berlogika 0). Karena gerbang AND memiliki output logika ‘0’ dan gerbang logika XOR memiliki output logika ‘1’, maka input gerbang OR akan berlogika ‘0’ dan ‘1’ sehingga gerbang OR akan memiliki output logika ‘1’ (output gerbang OR akan berlogika ‘1’ jika semua atau salah satunya

inputnya berlogika ‘1’). Karena output gerbang logika OR berlogika ‘1’, maka

menyebabkan LED menjadi aktif.

Kedua

rangkaian pada

percobaan 2 ini akan membentuk

output yang sama dengan

beberapa kondisi input awal sesuai yang terdapat pada jurnal.

Jika rangkaian A memiliki ouput logika 1 maka rangkaian B juga akan memiliki

output logika 1. Sebaliknya, jika rangkaian A memiliki ouput logika 0 maka

rangkaian B juga akan memiliki output logika 0.

Percobaan 2:

1.

Jelaskan bagaimana mendapatkan H1 dan H2 menggunakan aljabar Boolean dan Peta

Karnaugh

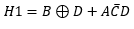

Pada percobaan 2, untuk mendapatkan H1 dan H2 menggunakan aljabar Boolean

dan Peta Karnaugh, dapat dilakukan

Pada percobaan 2 terdapat dua buah rangkaian.

Rangkaian pertama memiliki input awal B, D, A, C’, dan D. Sedangkan untuk rangkaian

kedua memiliki input awal B, D, A, B, dan C’. Inputan awal B dan D melewati

gerbang logika XOR, sedangkan input dari A, C’, dan D melewati gerbang

logika AND. Kemudian output dari BD dan AC’D akan melewati gerbang

logika OR untuk menentukan kondisi output dari rangkaian.

Kondisi 1

Berdasarkan data pada tabel nomor 1, untuk kondisi 1 memiliki input awal yaitu A=0, B=0, C=0,

dan D=0. Sehingga didapatkan:

Keterangan:

B ⊕ D = B dan D terhubung ke gerbang XOR

C’ = Input C’ adalah kebalikan dari input C

Dari hasil perhitungan di atas, maka

didapatkan:

Dari

perhitungan tersebut dapat disimpulkan bahwa hasil H1 dan H2 yang didapatkan

dari simulasi rangkaian dengan hasil perhitungan dari persamaan adalah sama

yaitu berlogika ‘0’.

Kondisi 2

Berdasarkan data pada tabel nomor 2, untuk kondisi

2 memiliki input awal yaitu A=1, B=0, C=0, dan D=0. Sehingga didapatkan:

Keterangan:

B ⊕ D = B dan D terhubung ke gerbang XOR

C’ = Input C’ adalah kebalikan dari input C

Dari hasil perhitungan di atas, maka

didapatkan:

Dari

perhitungan tersebut dapat disimpulkan bahwa hasil H1 dan H2 yang didapatkan

dari simulasi rangkaian dengan hasil perhitungan dari persamaan adalah sama

yaitu berlogika ‘0’.

Kondisi 3

Berdasarkan data pada tabel nomor 3, untuk kondisi

3 memiliki input awal yaitu A=0, B=1, C=0, dan D=0. Sehingga didapatkan:

Keterangan:

B ⊕ D = B dan D terhubung ke gerbang XOR

C’ = Input C’ adalah kebalikan dari input C

Dari

perhitungan tersebut dapat disimpulkan bahwa hasil H1 dan H2 yang didapatkan

dari simulasi rangkaian dengan hasil perhitungan dari persamaan adalah sama

yaitu berlogika ‘1’.

Berdasarkan analisa di atas, dapat disimpulkan bahwa hasil H1

dan H2 didapat dengan menggunakan aljabar Boolean dan Peta Karnaugh. Rangkaian 1

dan rangkaian 2 pada percobaan 2 ini merupakan penyederhanaan dari aljabar

Boolean dan Peta Karnaugh. Pada

percobaan 2 ini, terdapat dua buah rangkaian yang memiliki hasil output yang

sama dengan beberapa

kondisi input yang diberikan sesuai dengan jurnal. Hal ini terjadi karena rangkaian secara keseluruhan

merupakan penyederhanaan dengan 2 rumus yang berbeda, tetapi tetap memiliki

hasil output yang sama. Sehingga dapat dibuktikan bahwa terdapat kesamaan hasil H1

dan H2 yang didapatkan dari penyederhanaan dengan aljabar Boolean dan Peta

Karnaugh.

Tidak ada komentar:

Posting Komentar